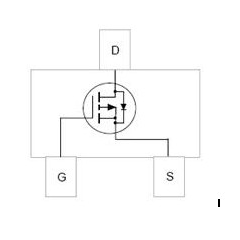

На първо място, типът и структурата на MOSFET, MOSFET е FET (друг е JFET), може да бъде произведен в подобрен или изчерпващ тип, P-канал или N-канал общо четири типа, но действителното приложение само на подобрен N -канални MOSFET и подобрени P-канални MOSFET, така че обикновено наричани NMOSFET или PMOSFET се отнася до така обикновено споменатия NMOSFET или PMOSFET се отнася за тези два вида. За тези два типа подобрени MOSFET транзистори, NMOSFET се използват по-често поради ниското им съпротивление и лекотата на производство. Следователно NMOSFET обикновено се използват в импулсно захранване и приложения за моторно задвижване и следващото въведение също се фокусира върху NMOSFET. съществува паразитен капацитет между трите извода наMOSFET, което не е необходимо, а по-скоро поради ограниченията на производствения процес. Наличието на паразитен капацитет прави малко трудно проектирането или избора на драйверна верига. Между дрейна и сорса има паразитен диод. Това се нарича телесен диод и е важен при задвижване на индуктивни товари като двигатели. Между другото, основният диод присъства само в отделни MOSFET транзистори и обикновено не присъства в IC чип.

Сега наMOSFETзадвижване на приложения с ниско напрежение, когато използването на 5V захранване, този път, ако използвате традиционната структура на тотемния стълб, поради транзистора е около 0.7V спад на напрежението, което води до действителното крайно добавяне към портата на напрежението е само 4,3 V. Понастоящем избираме номиналното напрежение на портата от 4,5 V на MOSFET при съществуването на определени рискове. Същият проблем възниква при използване на 3V или други случаи на захранване с ниско напрежение. Двойно напрежение се използва в някои управляващи вериги, където логическата секция използва типично 5V или 3,3V цифрово напрежение, а захранващата секция използва 12V или дори по-високо. Двете напрежения са свързани с обща маса. Това поставя изискване да се използва верига, която позволява на страната с ниско напрежение да контролира ефективно MOSFET от страната с високо напрежение, докато MOSFET от страната с високо напрежение ще се изправи пред същите проблеми, споменати в 1 и 2.

И в трите случая структурата на тотемния стълб не може да отговори на изходните изисквания и много готови интегрални схеми на драйвери на MOSFET не изглежда да включват структура за ограничаване на напрежението на портата. Входното напрежение не е фиксирана стойност, то варира с времето или други фактори. Тази вариация води до нестабилност на задвижващото напрежение, предоставено на MOSFET от PWM веригата. За да направят MOSFET безопасен от високи напрежения на портата, много MOSFET имат вградени регулатори на напрежението, за да ограничат принудително амплитудата на напрежението на портата. В този случай, когато напрежението на задвижването е по-голямо от регулатора на напрежението, това ще доведе до голяма статична консумация на енергия в същото време, ако просто използвате принципа на резисторния делител на напрежението, за да намалите напрежението на портата, ще има относително високо входно напрежение, наMOSFETработи добре, докато входното напрежение се намалява, когато напрежението на гейта е недостатъчно, за да причини непълна проводимост, като по този начин се увеличава консумацията на енергия.

Относително често срещана верига тук само за веригата на драйвера NMOSFET за извършване на прост анализ: Vl и Vh са захранването от нисък и висок клас, двете напрежения могат да бъдат еднакви, но Vl не трябва да надвишава Vh. Q1 и Q2 образуват обърнат тотем, използван за реализиране на изолацията и в същото време за гарантиране, че двете задвижващи тръби Q3 и Q4 няма да имат една и съща времева проводимост. R2 и R3 осигуряват PWM напрежение R2 и R3 осигуряват PWM референтното напрежение, като промените това еталонно, можете да оставите веригата да работи в PWM сигналната форма на вълната е сравнително стръмна и права позиция. Q3 и Q4 се използват за осигуряване на задвижващ ток, поради времето на включване, Q3 и Q4 спрямо Vh и GND са само минимален спад на напрежението Vce, този спад на напрежението обикновено е само 0,3 V или така, много по-нисък от 0,7 V Vce R5 и R6 са резисторите за обратна връзка, използвани за порта R5 и R6 са резистори за обратна връзка, използвани за проба на напрежението на портата, което след това преминава през Q5 за генериране на силна отрицателна обратна връзка на базите на Q1 и Q2, като по този начин ограничават напрежението на затвора до крайна стойност. Тази стойност може да се регулира от R5 и R6. И накрая, R1 осигурява ограничението на базовия ток към Q3 и Q4, а R4 осигурява ограничението на тока на затвора към MOSFET, което е ограничението на Ice на Q3Q4. Ускоряващ кондензатор може да бъде свързан паралелно над R4, ако е необходимо.